00:00:00

指令系统 原创

一、 指令系统(Instruction Set Architecture, ISA)

指令系统(Instruction Set Architecture, ISA),通常也被称为指令集、计算机架构 是一套详细的规范和标准,定义了计算机硬件能够识别和执行的基本操作指令的集合

1.1 指令格式

指令格式是指令的编码方式,一条指令通常包含和

- 操作码:指明操作的类型,如算术运算(加、减、乘、除)、逻辑运算(与、或、非)、数据传送(加载、存储)、控制流(跳转、调用、返回)等

- 操作数/地址码:提供操作的、提供结果的、提供程序执行的目标位置

1.2 指令操作数的寻址方式

- (Immediate Addressing)

- 核心思想:操作数。指令的操作数字段不是地址,就是数据本身。

- 工作原理:CPU从指令流中取出指令后,操作数部分,无需再次访问内存或寄存器。

- 优点:,因为取指后立即得到操作数。

- 缺点:数值的大小和范围,不灵活。

- (Direct Addressing)

- 核心思想:指令的操作数字段直接给出的是操作数在。

- 工作原理:CPU根据指令中给出的地址,即可从该地址读取或写入操作数。

- 优点:。

- 缺点:地址空间(例如16位操作数只能直接寻址64KB空间)。如果地址是固定的,程序移植性差。

- (Register Addressing)

- 核心思想:操作数存放在中。

- 工作原理:指令中指定寄存器编号,CPU获取操作数。

- 优点:(比访问内存快多个数量级),(因为寄存器数量少,编号只需很少几位)。

- 缺点:可用的寄存器数量。

- (Register Indirect Addressing)

- 核心思想:指令中指定的里存放的,而是数据在。

- 工作原理:CPU,拿到有效地址(EA),然后根据这个地址,才能取得最终的操作数。

- 优点:非常,通过改变就可以访问,常用于处理数组、字符串、指针等。

- 缺点:需要(一次读寄存器,一次读内存),比直接寄存器寻址慢。

- (Register Relative Addressing) 或

- 核心思想:操作数的有效地址由一个的内容加上一个 形成。

EA = (Base Register) + Offset - 工作原理:偏移量直接,是一个常数。CPU和,再去访问内存。

- 优点:非常适合访问和。基址寄存器可以指向结构/数组的起始地址,偏移量用来访问特定字段/元素。

- 核心思想:操作数的有效地址由一个的内容加上一个 形成。

- (Indexed Addressing)

- 核心思想:与,通常使用一个(如SI, DI)的内容加上一个(可能在指令中,也可能在另一个寄存器中)来形成有效地址。

EA = Base + (Index Register) - 工作原理:变址寄存器的值通常作为数组的索引(0, 1, 2...),通过改变它的值来遍历数组。

- 优点:是。只需在循环中改变变址寄存器的值即可。

- 核心思想:与,通常使用一个(如SI, DI)的内容加上一个(可能在指令中,也可能在另一个寄存器中)来形成有效地址。

注意

现代处理器中,和的界限已经很模糊,常被统称为。

- (Based Indexed Addressing)

- 核心思想:有效地址由一个的内容加上一个的内容共同形成。

EA = (Base Register) + (Index Register) - 工作原理:基址寄存器指向一个基地址(如数组起始),变址寄存器提供索引偏移。

- 优点:极其灵活,非常适合访问或。基址寄存器可以指向不同的行(或不同的结构体),变址寄存器指向行内的列(或结构体内的字段)。

- 缺点:需要。

- 核心思想:有效地址由一个的内容加上一个的内容共同形成。

小结

| 寻址方式 | 有效地址 (EA) 计算 | 优点 | 缺点 | 常见用途 |

|---|---|---|---|---|

| 立即寻址 | 操作数 = 指令中的立即数 | 初始化、常量操作 | ||

| 直接寻址 | EA = 指令中的地址码 | 访问全局静态变量 | ||

| 寄存器寻址 | 操作数在指令指定的寄存器中 | 局部变量、中间结果 | ||

| 寄存器间接寻址 | EA = (寄存器) | ,可指向任何位置 | 需访问(取指后) | 指针、动态数据 |

| 寄存器相对寻址 | EA = (基址寄存器) + 偏移量 | 适合 | - | 访问数组元素、结构体字段 |

| 变址寻址 | EA = 基地址 + (变址寄存器) | 适合 | - | 循环操作数组 |

| 基址加变址寻址 | EA = (基址寄存器) + (变址寄存器) | ,适合二维结构 | 二维数组、结构体数组 |

1.3 指令系统分类

指令系统分为:复杂指令集(CISC:Complex Instruction Set Computer)和精简指令集(RISC:Reduced Instruction Set Computer)对比如下表所示

| 特性维度 | 📚 CISC (复杂指令集) | ✨ RISC (精简指令集) |

|---|---|---|

| 设计哲学 | 复杂、庞大 | 、指令简单高效,编译器组合功能 |

| 指令数量 | (数百条),包含大量专用指令 | (通常<100条),仅保留最常用指令 |

| 指令长度 | (1-15字节不等),灵活但译码复杂 | (通常32位),译码简单,利于流水线 |

| 内存访问 | 可直接操作内存数据 | 指令可访问内存 |

| 执行周期 | (1到上百周期),难以预测 | 完成,规律性强 |

| 指令使用率 | (80%时间只用20%指令) | ,每条指令都常用 |

| 寄存器数量 | (如x86: 8-16个),导致更多内存访问 | (通常32个),减少内存访问 |

| 控制方式 | 控制,灵活但有转换开销 | 控制,速度快 |

| 流水线支持 | :变长指令、周期不一导致流水线易阻塞 | :固定长度、单周期完美支持流水线 |

1.4 指令的执行方式

指令的执行方式有顺序、重叠、和流水方式三种

1.4.1 顺序执行

这是最简单、最原始的执行方式。

- 工作过程:

- 取出第k条指令。

- 执行第k条指令。

- 只有第k条指令后,才能开始取出第k+1条指令。

- 优点:

- ,硬件实现容易。

- 缺点:

- 。CPU的各功能部件(如取指部件、执行部件)在大部分时间内是串行工作的,利用率很低。例如,在执行指令时,取指部件是空闲的。

1.4.2 重叠执行

为了提升效率,让不同部件同时工作,这就产生了重叠执行方式。 "取指k+1" 和 "执行k" 这两个分别由不同部件完成的操作,可以同时进行。

- 工作过程:

- 在指令。

- 优点:

- 相比于顺序方式,。它缩短了指令的平均执行时间,使CPU功能部件的利用率提升。

- 缺点:

- 需要解决:如果"执行k"和"取指k+1"都需要访问内存,就会发生冲突(因为一个内存通常只有一个端口)

1.4.3 流水执行方式(指令流水线)

流水方式是重叠方式的并行思想的进一步发展和升华。它将指令的整个执行过程,每个的功能部件完成。

工作过程(以经典5段流水线为例):

- 取指(IF):从指令缓存取指令。

- 译码/读寄存器(ID):译码并从寄存器堆读取操作数。

- 执行(EX):在ALU中进行计算或地址计算。

- 访存(MEM):访问数据缓存(如果是Load/Store指令)。

- 写回(WB):将结果写回寄存器。

- 每个阶段完成后,指令及其结果被传递到下一阶段,就像在流水线上一样。

优点:

- ,大幅提高了指令的吞吐率(Throughput)。。

缺点 & 挑战:

- ,这些冒险会破坏流水线的流畅性,导致性能下降:

- :两条指令争抢同一个硬件资源(如同时访存)。

- :后一条指令需要前一条指令的计算结果,但结果还未产生( 是主要问题)。

- :遇到分支指令时,无法确定下一条指令的地址,导致流水线停顿。

- 解决冒险需要增加等复杂硬件机制。

- ,这些冒险会破坏流水线的流畅性,导致性能下降:

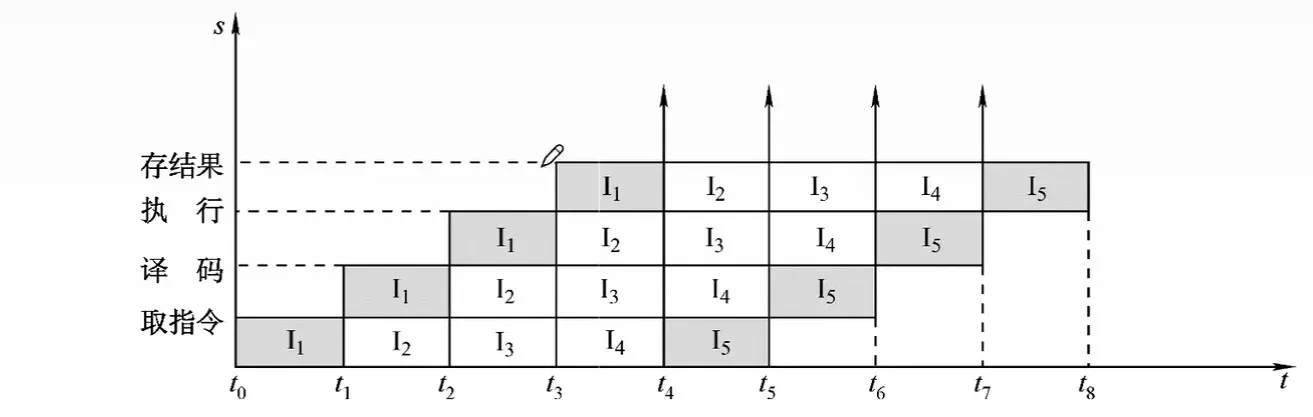

时空图:

从第5个时钟周期开始,每个周期都有一条指令完成(WB)。

1.4.4 小结

| 特性 | 顺序方式 | 重叠方式 | 流水方式 |

|---|---|---|---|

| 本质 | 串行执行 | ||

| 并行度 | 无 | ||

| 控制逻辑 | 简单 | ||

| 效率 | 最低 |

1.5

设流水线执行周期为 ,流水线每个部分执行完成的时间为 ,1条指令执行所需时间的 , 指令条数为 ,执行 条指令所花的时间为

1.5.1 常用公式

- 流水线周期计算公式为

- 1条指令执行的时间

- 流水线执行时间

- 流水线的吞吐率( ):在内流水线所的任务教量或输出结果数量

- 流水线的加速比( ):完成同样一批任务,不使用流水线的执行的时间与使用流水线的执行时间之比

1.5.2 计算示例

若指令流水线,把一条指全分为取指,分析,执行三部分,三部分的执行时间2ns, 2ns,1ns。

- 问:流水线周期是多少?100条指今全部执行完毕需要多久?求流水线的吞吐率是多少?流水线的加速比是多少?

- 答:

- 流水线周期:

- 100条指今全部执行完毕时间:

- 流水线吞吐率:

- 流水线的加速比: